如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

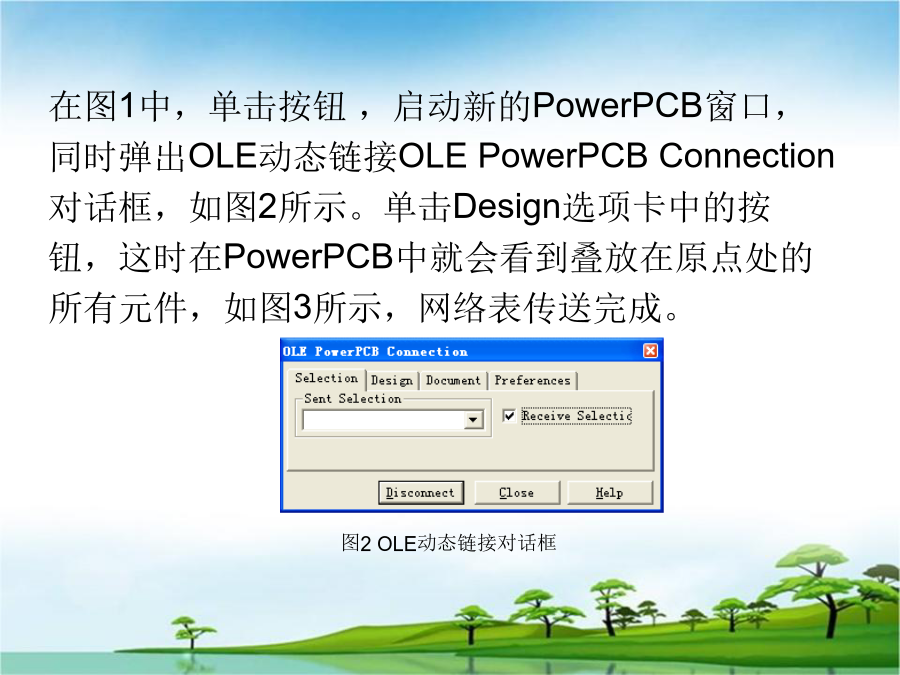

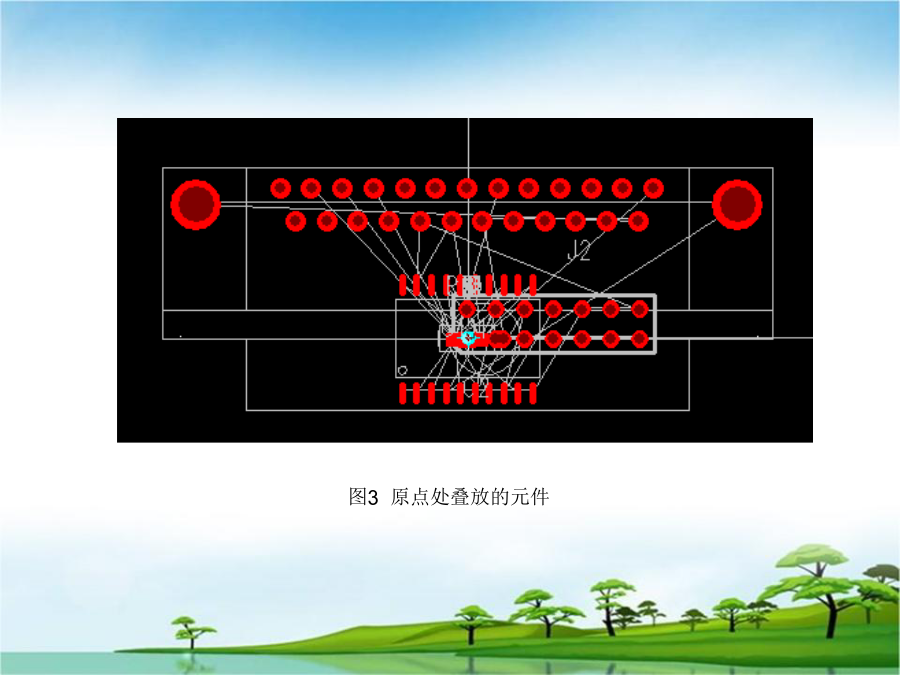

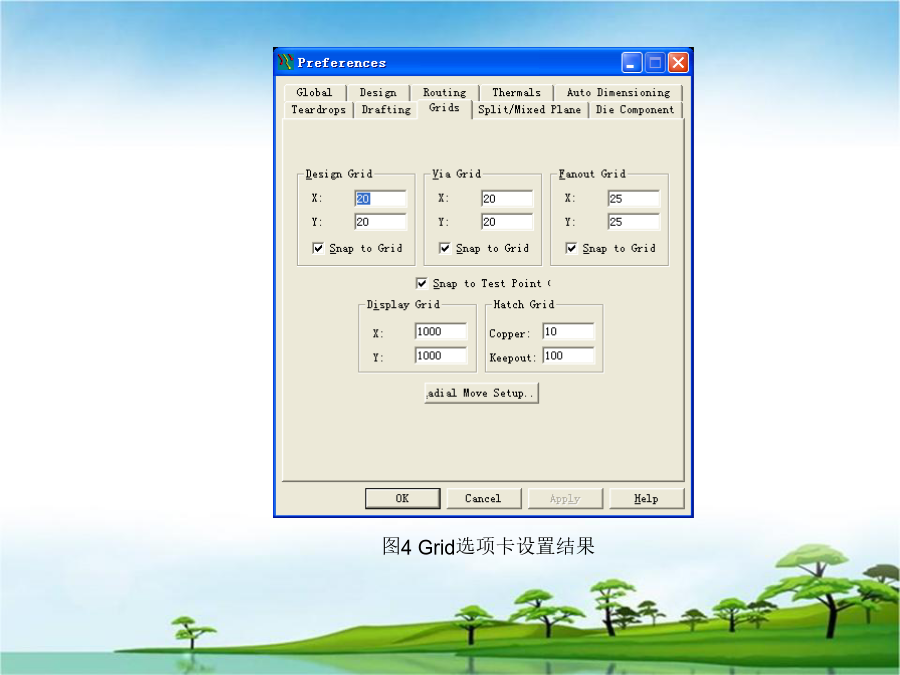

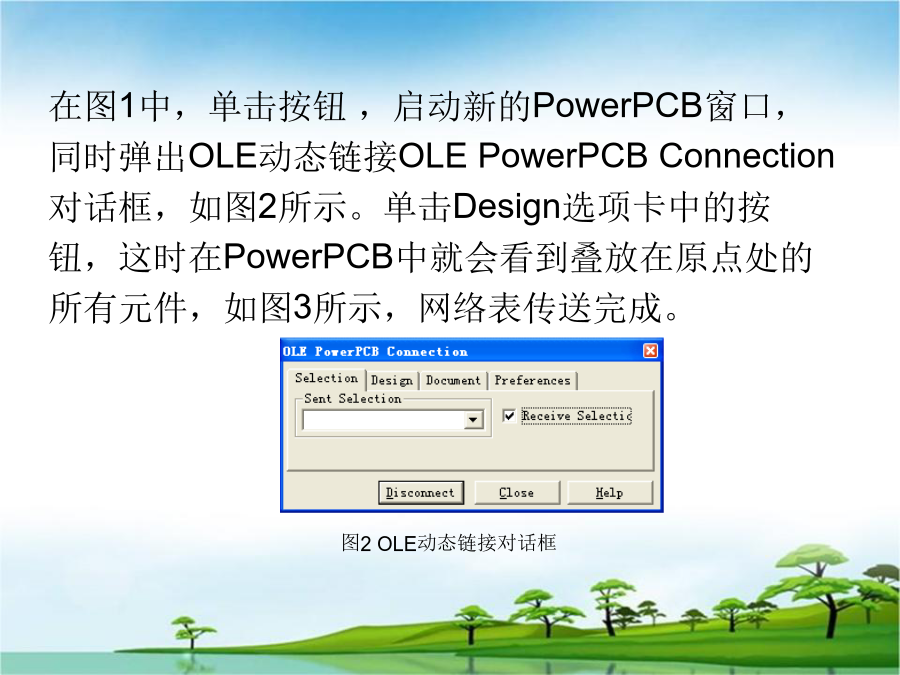

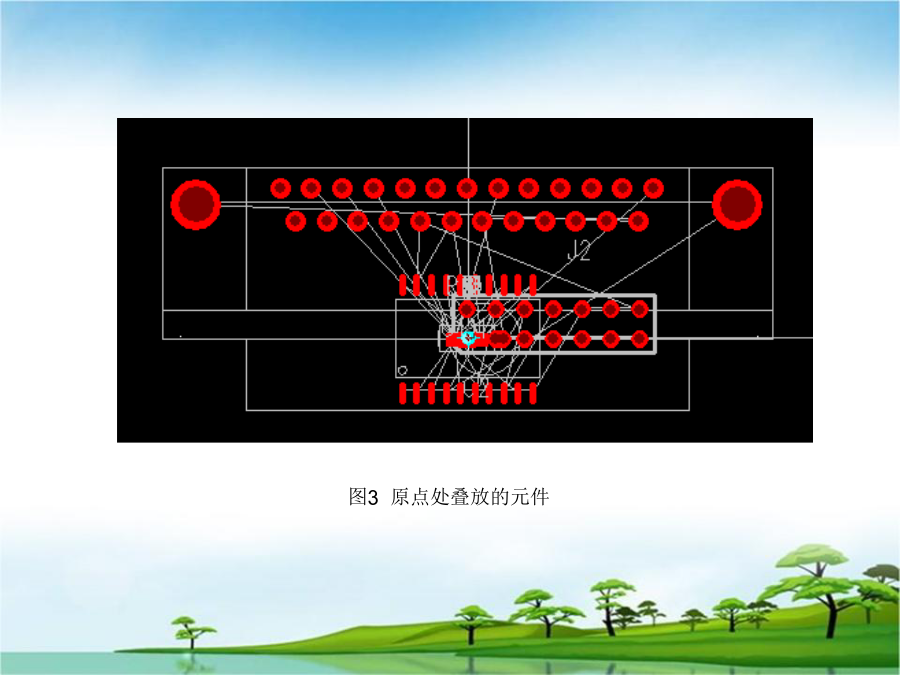

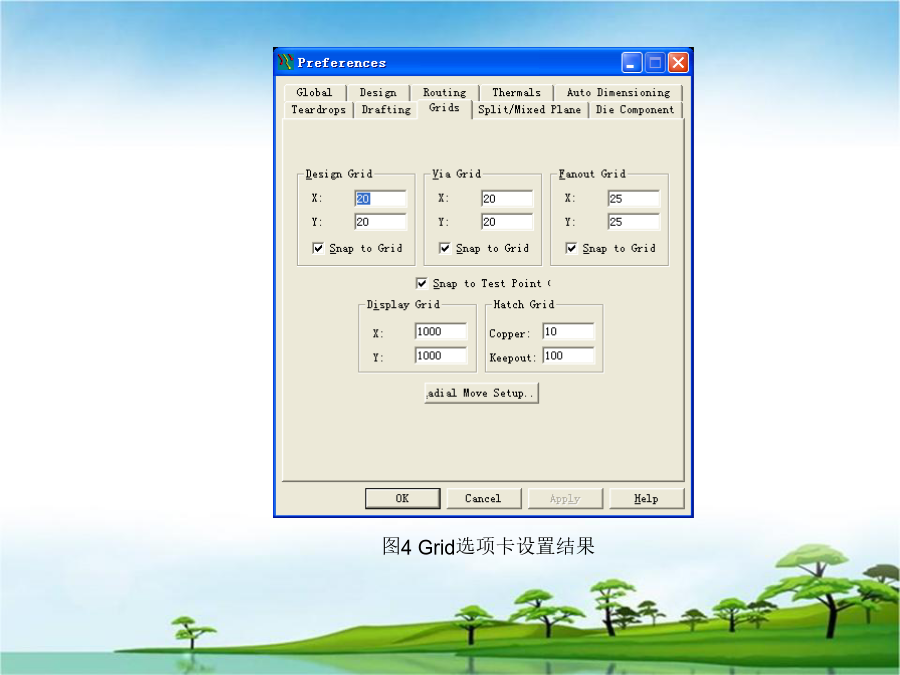

JTAG调试器的PCB设计1、网络表导入启动PowerPCB设计窗口,单击Tools|OLEPowerPCBConnection命令,弹出ConnecttoPowerPCB对话框,如图1所示(注:操作该步骤时确认没有启动PowerPCB设计窗口)。图1连接到PowerPCB对话框在图1中,单击按钮,启动新的PowerPCB窗口,同时弹出OLE动态链接OLEPowerPCBConnection对话框,如图2所示。单击Design选项卡中的按钮,这时在PowerPCB中就会看到叠放在原点处的所有元件,如图3所示,网络表传送完成。图2OLE动态链接对话框图3原点处叠放的元件2.相关参数设置(1)PowerPCB设计环境参数设置在Global选项卡中,将DesignUnits中的单位设置为Mils。其他参数使用软件默认值。Grid选项卡设置如图4所示:图4Grid选项卡设置结果(2)Net显示设置在PowerPCB设计窗口,单击View|Nets命令,打开ViewNets对话框,选择+5V单击add将+5v添加到View窗口,在View窗口中选中+5V,这时颜色选项卡由灰色变成可选择的,接下来给电源网络选择黄色作为显示颜色,如图6所示。图5ViewNets设置对话框图6电源网络显示设置结果(3)绘制JTAG调试器电路板边框在PowerPCB设计窗口中,使用绘图工具盒中的绘制板框与切割加工区命令,绘制一个2200mil*1600mil的矩形电路板边框。(4)板层设置LayersSetup在PowerPCB设计窗口中,单击Setup|LayerDefinition命令,打开层定义对话框LayersSetup,如图7所示。软件默认板层是双面板,在顶层(Top)和底层(Bottom)之间没有任何层出现。JTAG调试器电路板为双面板。图7板层设置对话框(5)DesignRules设置在PowerPCB设计窗口中,单击Setup|DesignRules命令,弹出如图8所示的设计规则(Rules)窗口。单击Default打开默认规则对话框如图8所示。图8设计规则对话框图9默认规则设置对话框安全间距Clearance设置结果如图10所示:图10安全间距Clearance设置结果走线Routing设置结果如图11所示,该电路板为双面走线。图11走线Routing设置结果3.JTAG调试器元件布局使用设计工具盒中与元件布局相关的命令,进行元件的布局。首先选中元件J1将其移动到板框边缘,同时右击选择Query/Modify对话框,在Glued前打勾,将J1固定,其他元件均以该元件为参照进行布局,如图12所示。图12DB25移动结果另外,选中C1电容,右击在弹出的快速菜单中选择FlidSide将其放置于电路板的Bottom层,其余器件均处于Top层;为了让布局界面清晰,单击Setup|SelectedColor打开颜色设置选项卡,在Other框中将connection的颜色设置为黑色,当布局结束时,再将其修改为区别于背景的可见颜色,布局结果如图13所示。图13JTAG调试器布局结果(connection为黑色)图14JTAG调试器元件布局结果(connection为黄色)4.JTAG调试器布线在PowerPCB的软件中,单击Setup|Preferences|Design|On-LineDRC|PreventError命令,激活半自动布线功能。在布线过程中,当需要增加过孔时,按住shift键同时单击即可实现添加。打开设计工具盒,使用设计工具盒中的布线命令,最常用的是半自动布线命令DynamicRoute。单击半自动布线命令后,单击需要连线的焊盘,布线开始,JTAG调试器布线结果如图所示。图15JTAG调试器布线结果5.JTAG调试器灌铜区设置使用命令绘制灌铜区边框,修改灌铜区属性,将其指定给Bottom层,分配给地网络即将灌铜区指定为底层的地网络上。使用右键菜单中Flood命令,完成灌铜,结果如图16所示。图16JTAG调试器灌铜结果6.JTAG调试器电路的设计验证在PowerPCB的设计窗口中,单击Tools|VerifyDesign命令,打开设计验证窗口,在检查栏目Check下,单击Clearance|Start命令,提示发现错误,如图17所示。元件的PCB封装外框超过了电路板边框,在这里实际电路情况需要这样放置,可以不用修改,继续验证其它项目。图17与外框间距错误提示7.