如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

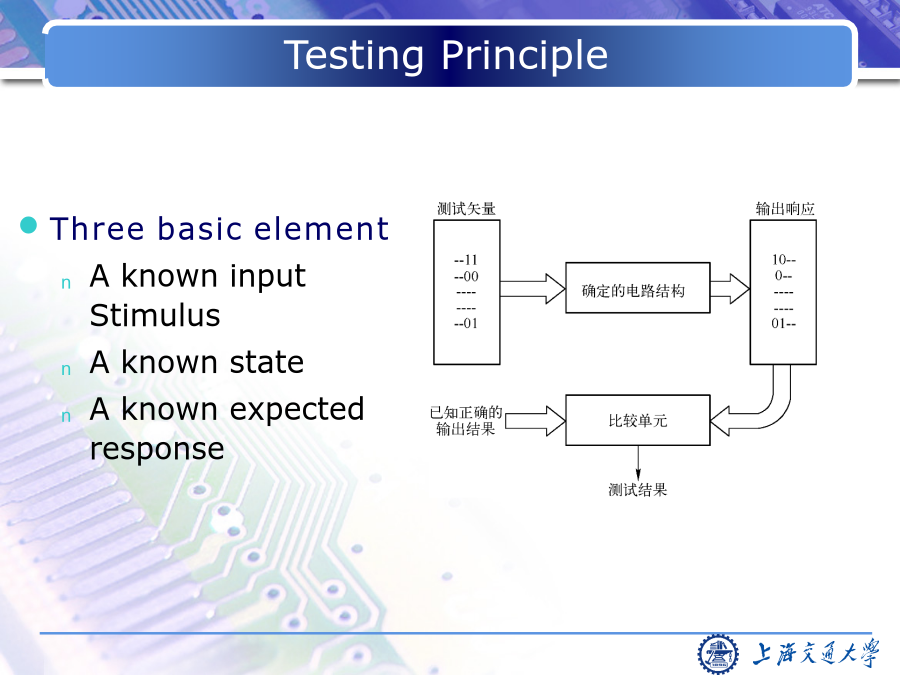

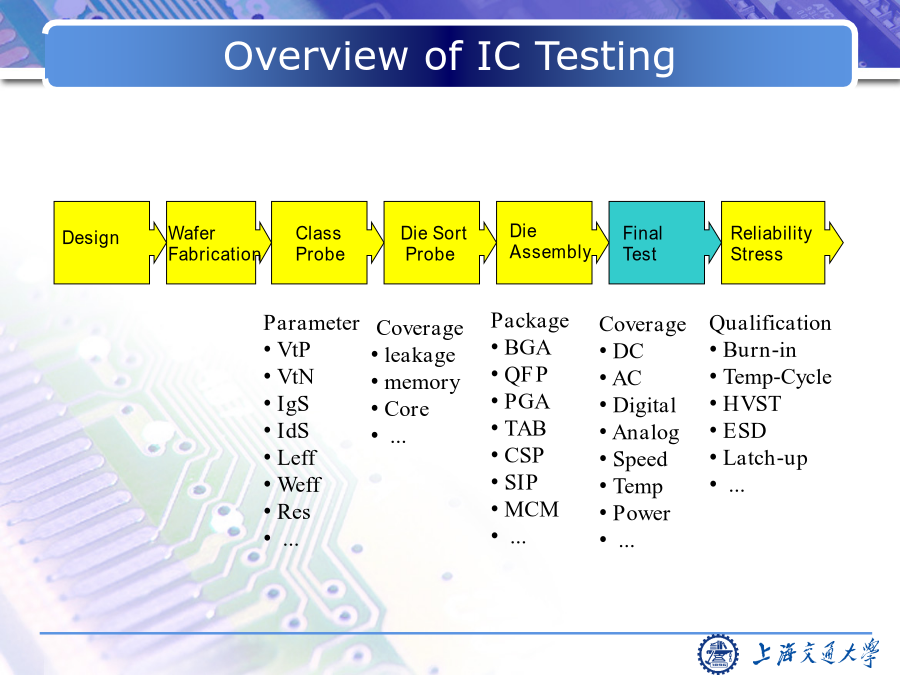

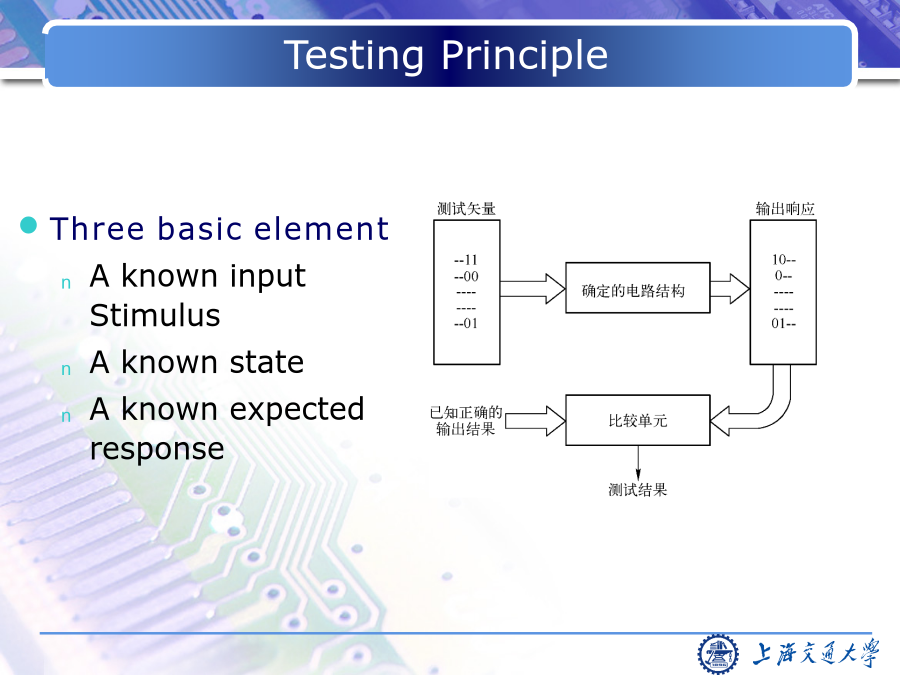

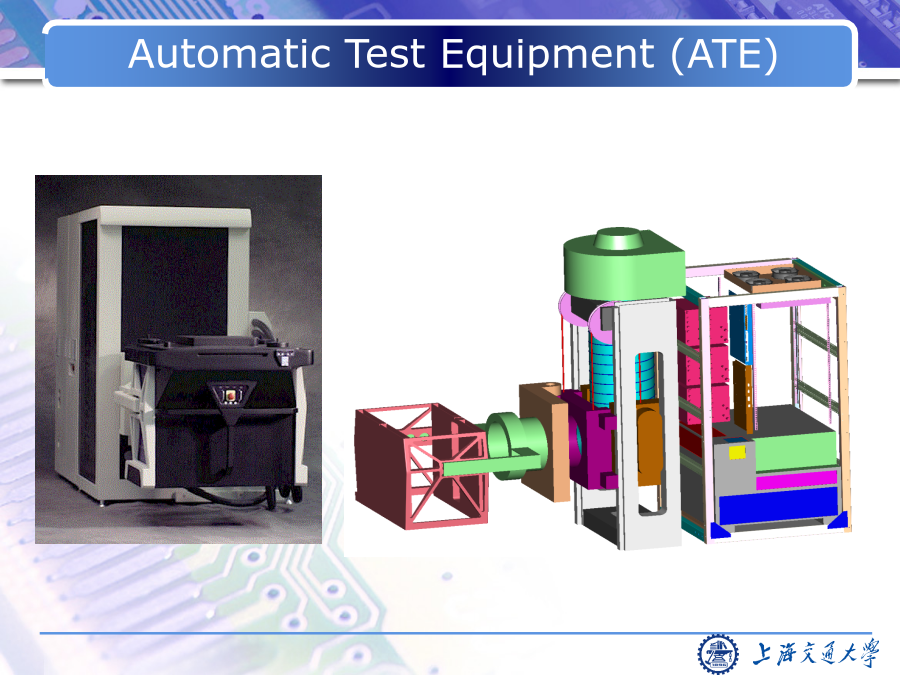

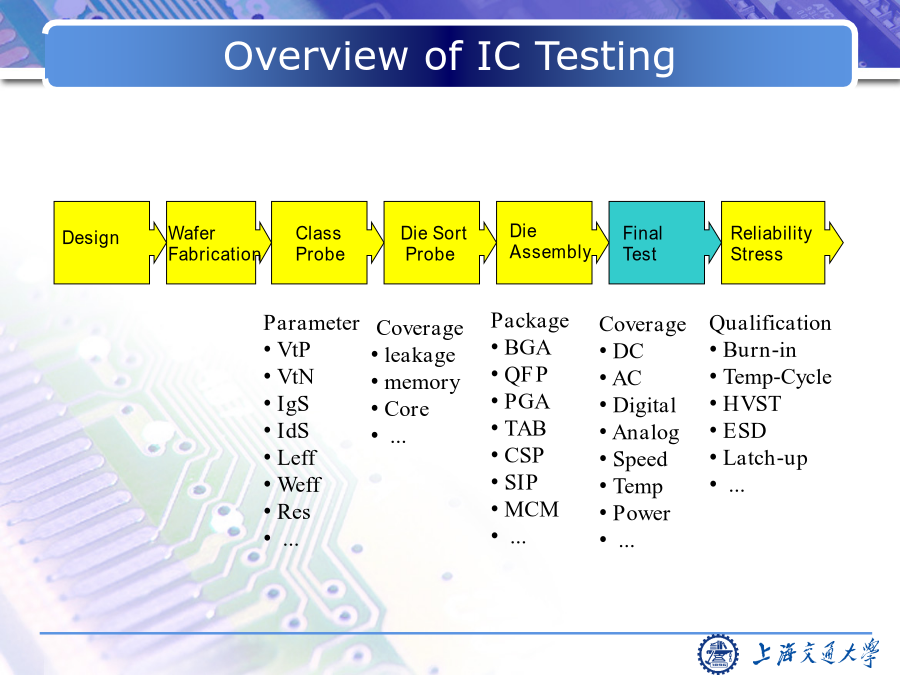

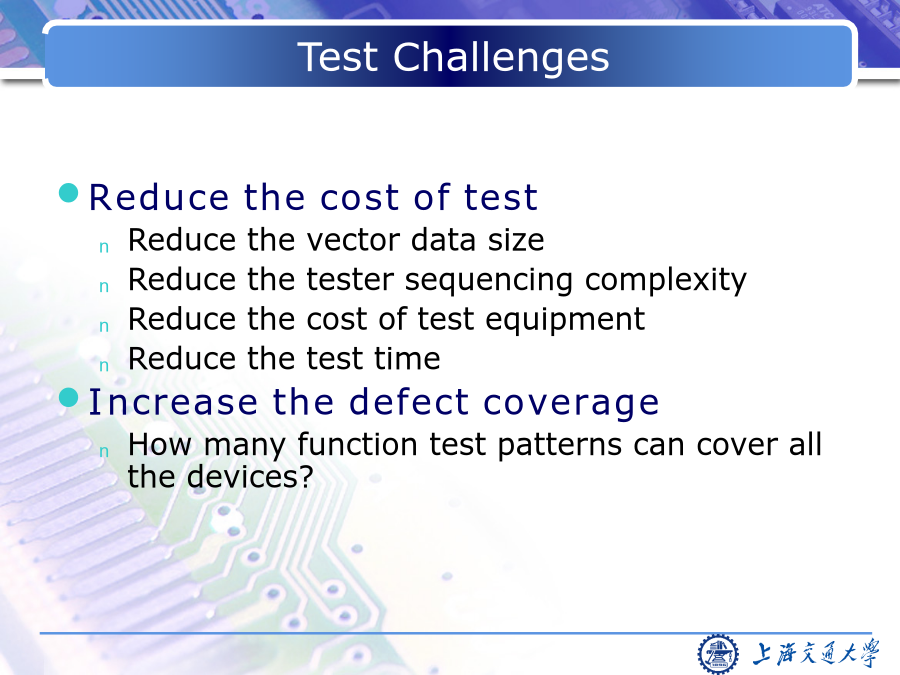

第十章OutlinesVerificationvs.TestTestingPrincipleAutomaticTestEquipment(ATE)OverviewofICTestingTestChallengesOutlinesTypesofTestVectorSetsWhyModelFaults?Defect&FaultModelingDefinitionDefect:shorttothegrandFault:signalbstuckatlogic0Error:happenswhena=1b=1FaultModelsStuck-ATFaultsTransitionDelayFaultPathDelayFaultMemoryFaultsMemoryFault–cont.OutlinesFaultCoverageTestGenerationDefinitionsVectorGenerationUsingATPGToolOutlinesWhatisDFT?WhyAddtestLogic?Pro&ConPerceptionsofDFTPopularDFTTechniquesforSoCTestingScanChainSequentialLogic–HardtoTest!StepsofScanDesignScanFlip-Flop(SFF)ScanChainConnectionTestSequentialLogicUsingScanToolsforScanSynthesisandATPGScanDesignRulesBasicScanDesignRulesExample:DealingwithTri-statebusExample:DealingwithBlackBoxExample:MemoryBlockInterfaceGeneralDFTConsiderationforSoCDesignPrepareScanwrappersfornon-synthesizablemodules,suchasmemoryblockAvoidlongscanchain,max1000FFsperchainAvoidpowerconsumptionissue,mayneedtoseparatethewholechiptofewscanmodesandtheclockstothemodulenotbeingtestedshouldbedisabledScanchainreorderingmayneedinlayoutstageScanOverhead:Scanpathimpacttiming,areaandpowergoalsModerateareaoverheadabout10%,speed5%Multiplexerdelayaddedincombinationalpath;approx.twogate-delaysFlip-flopoutputloadingduetooneadditionalfanout;approx.5-6%Atleastoneextrapinsforscanmodesignals:scan_mode,scan_enable,scan_clk,scan_reset,scan_in,scan_outScanDesignFlowTypicalQualityRequirementsSummaryMemoryBuild-in-selftest(MVIST)ImportanceofMemoryTestMemoryModelMemoryBuiltInSelfTest(MBIST)MemoryBuiltInSelfTest(MBIST)BasicTestPortsMemoryBISTAlgorithmsCheckerboardAlgorithmMarchAlgorithmAlgorithmMATSMATS+MATS++MARCHXMARCHC—MARCHAMARCHYMARCHBMarchTestComplexityRetentiontestingverifiesifmemorycellscanretaintheirinitialcontentsforacertainperiodoftime.Thetimeperiodcanvaryfrom10-80msdependingmainlyonthemanufacturingprocessandtheambienttemperatureduringthetestapplicationTheinserteddelaycanrefertotheAlgorithmMarchCandCheckerboardSharecontrollerwithmemoryblo