如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

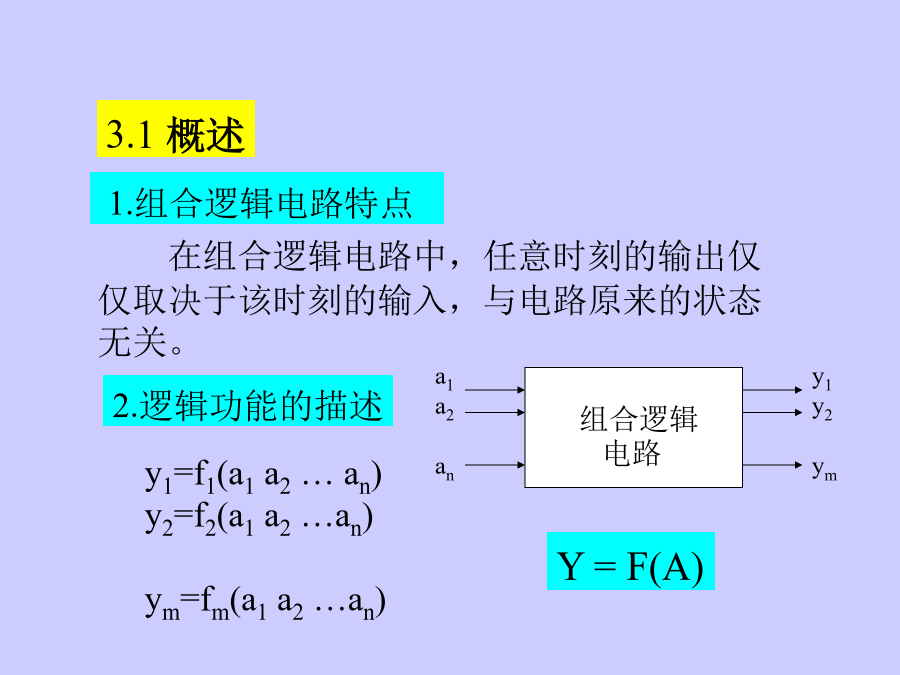

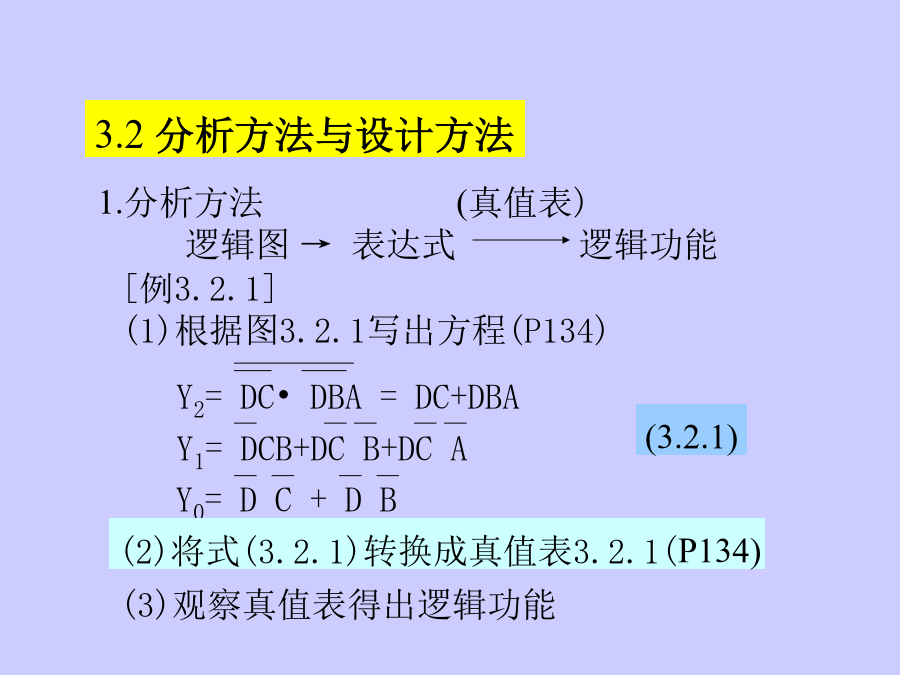

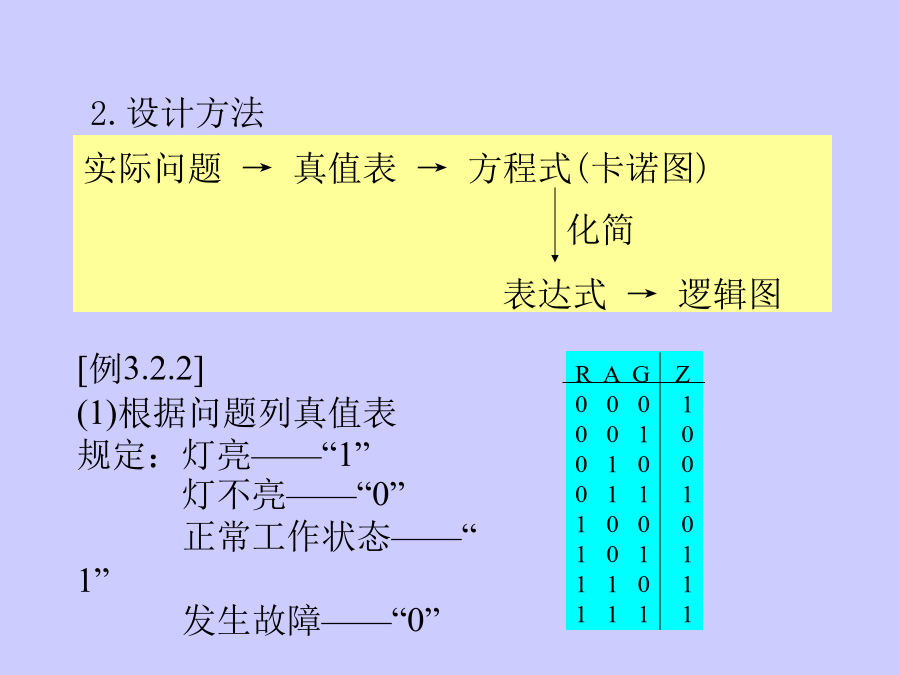

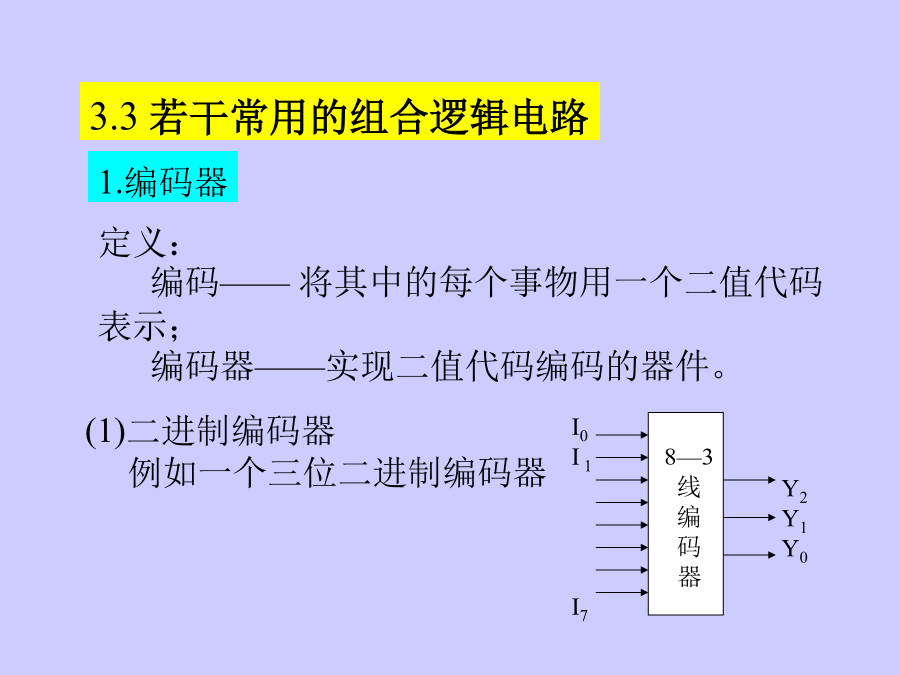

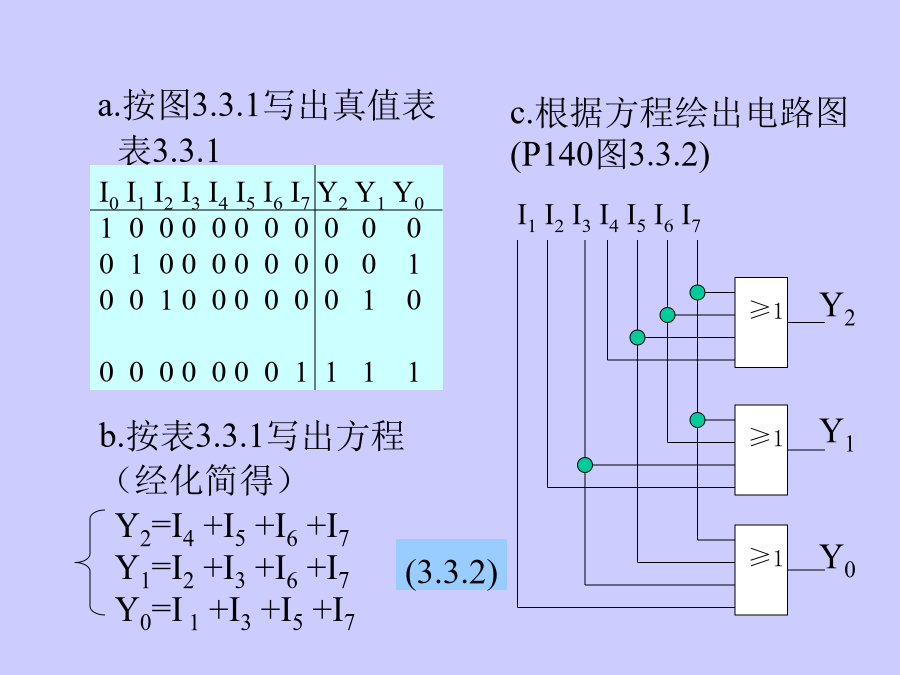

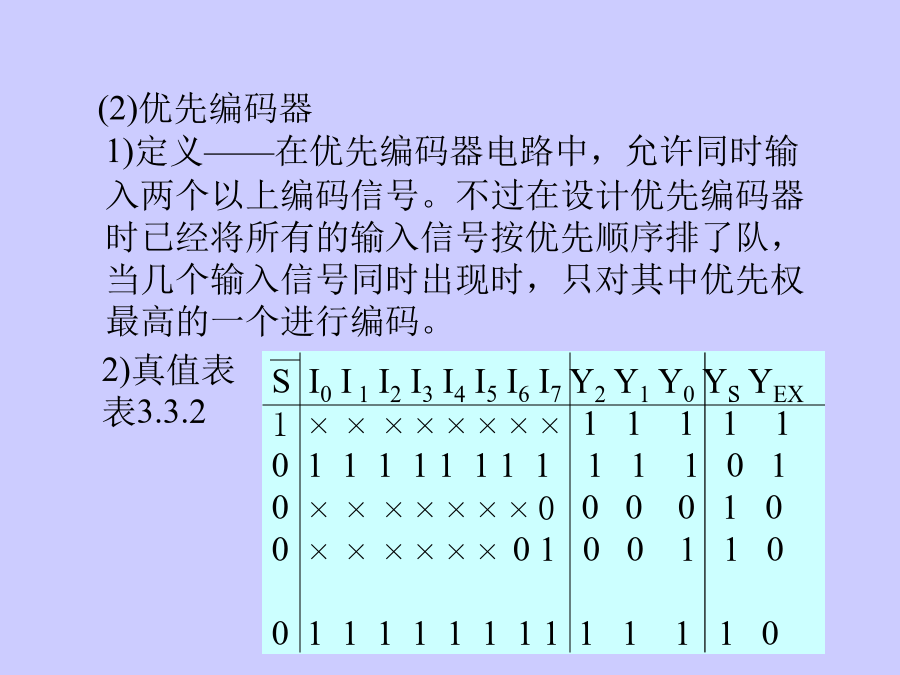

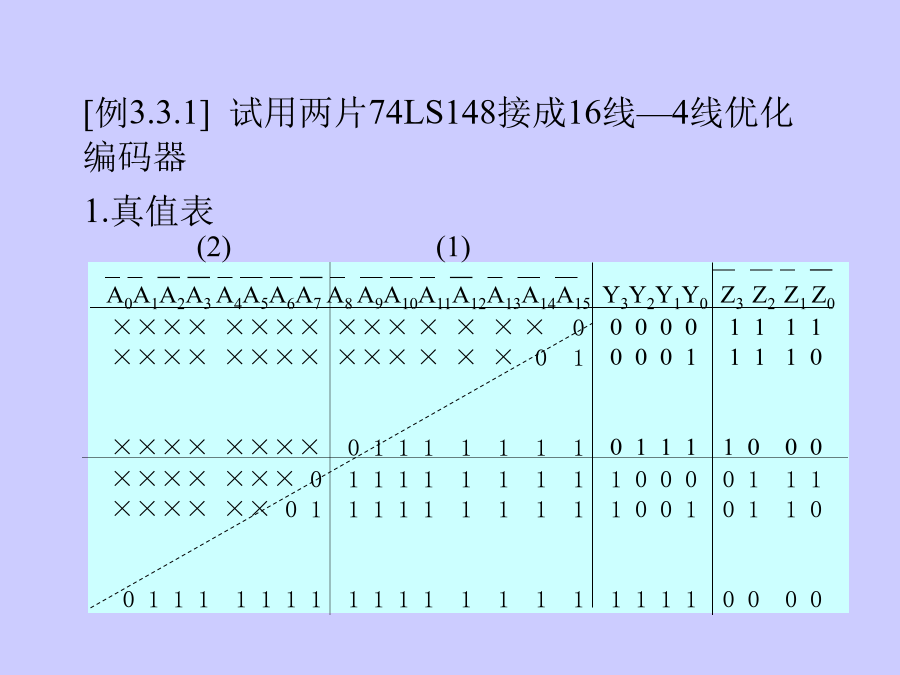

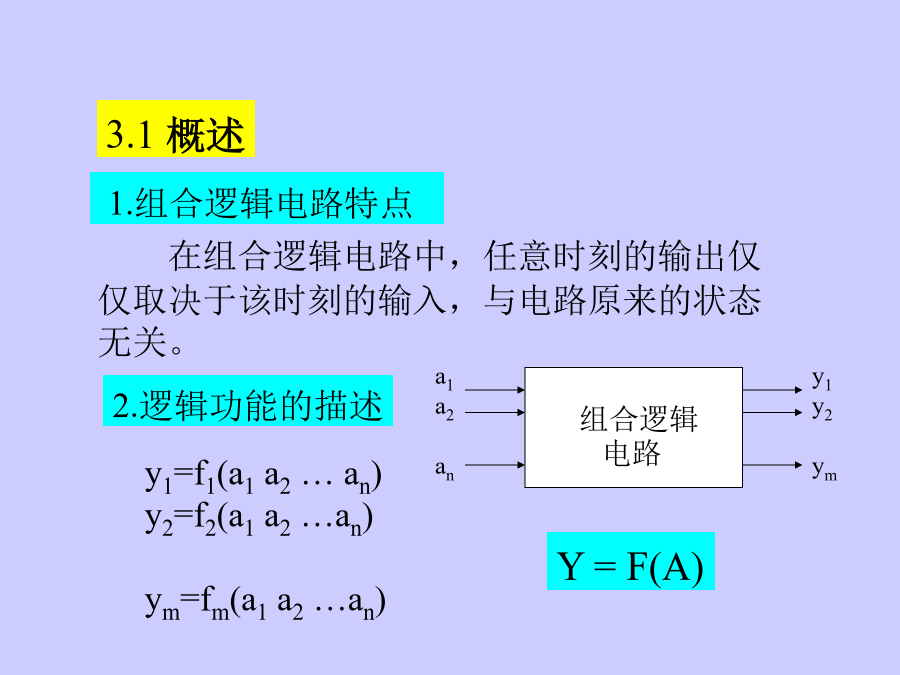

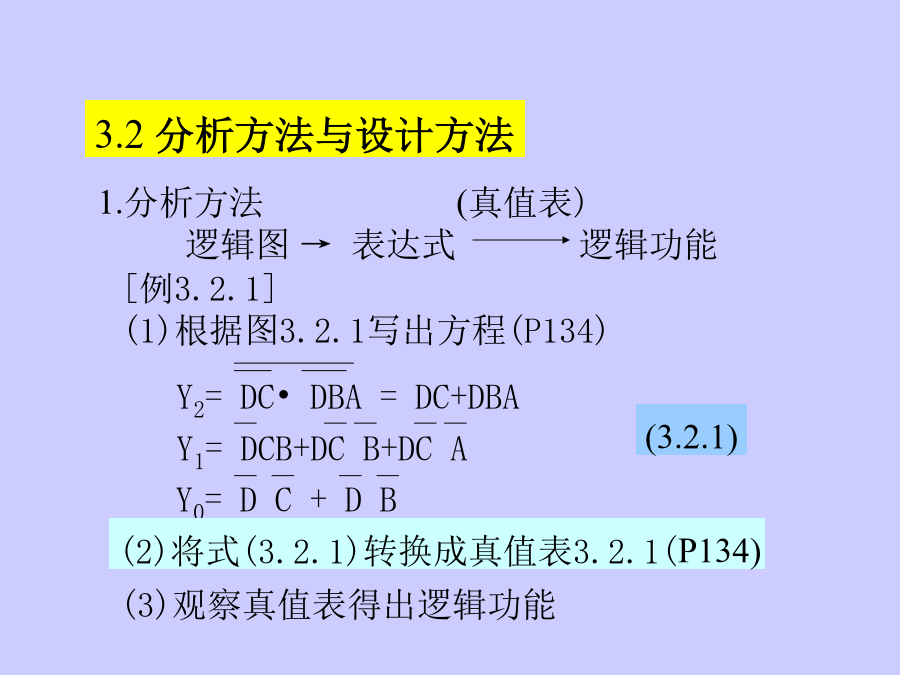

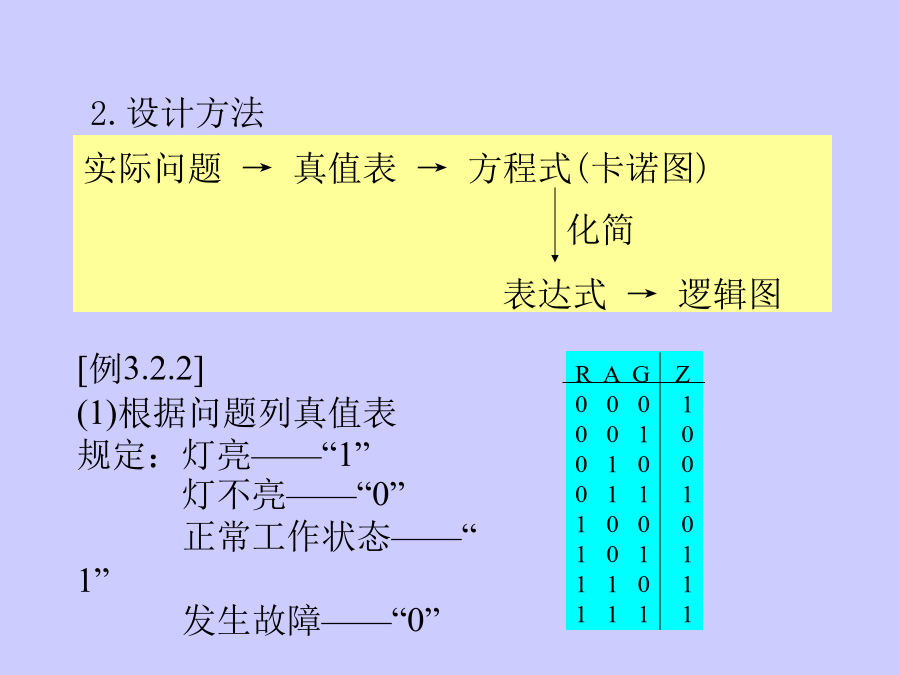

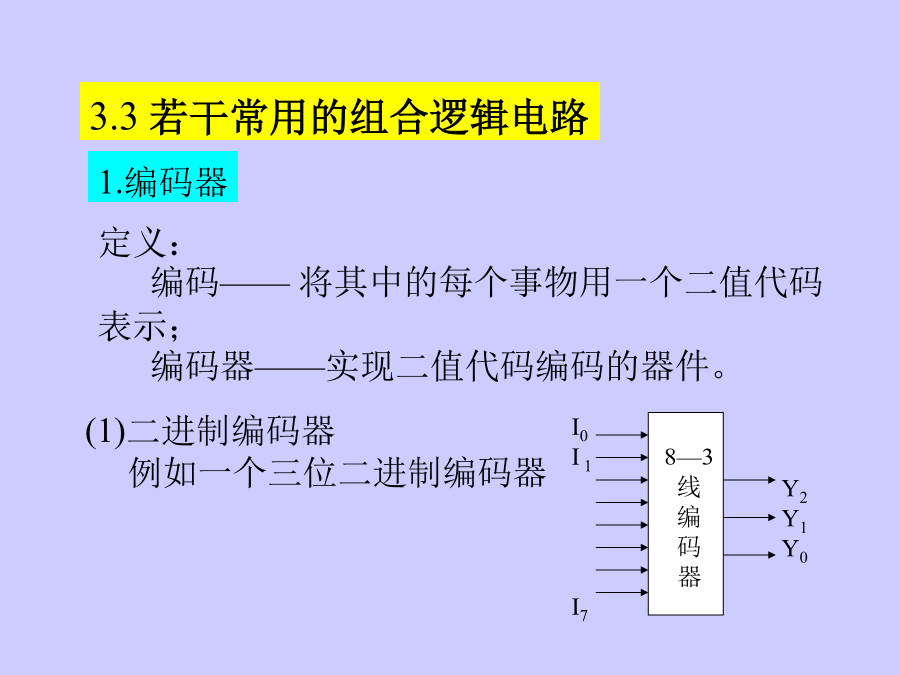

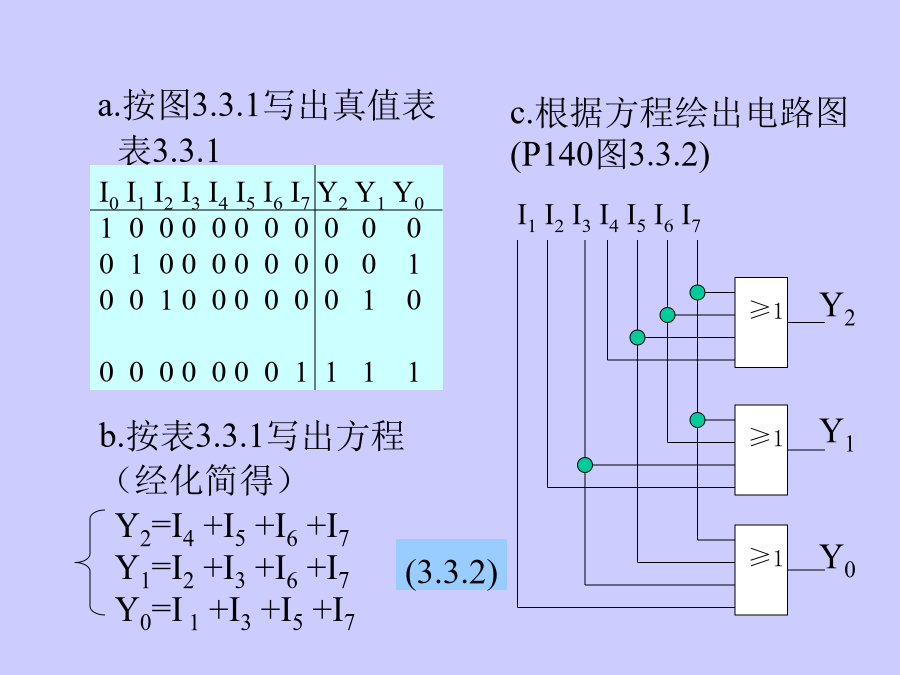

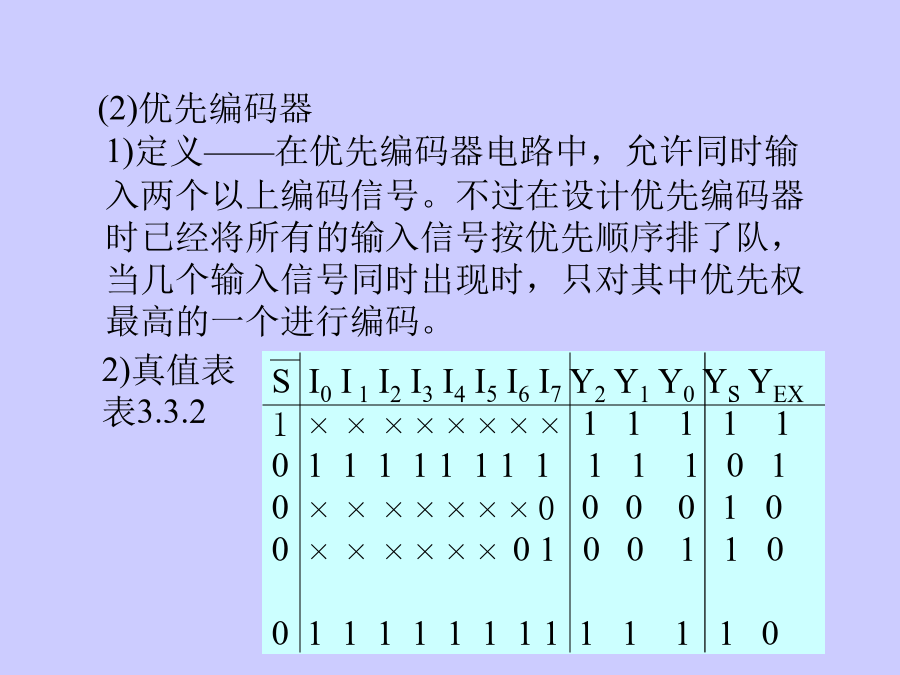

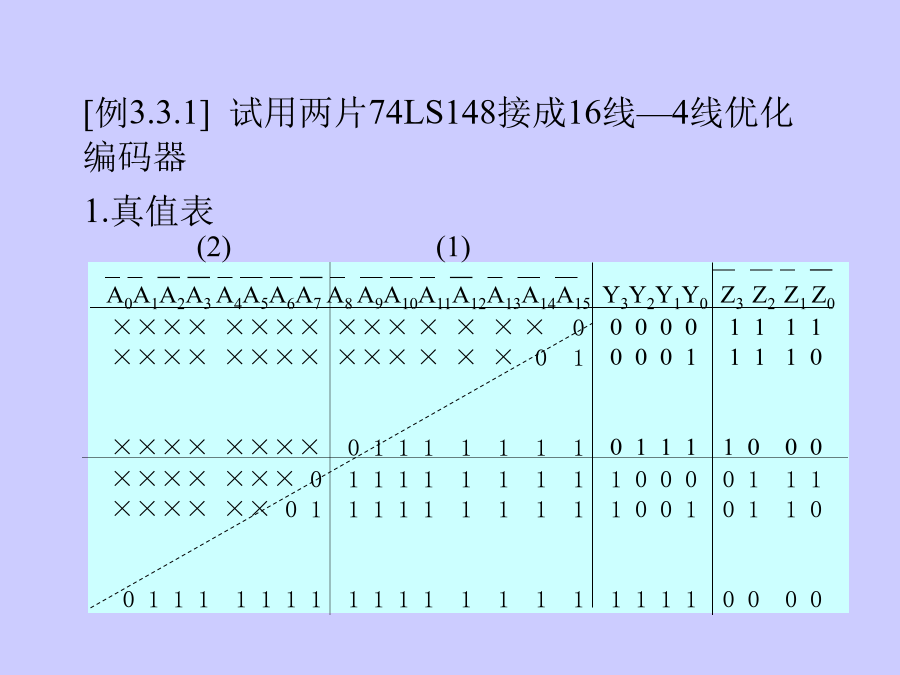

第三章组合逻辑电路3.1概述3.2分析方法与设计方法2.设计方法(2)根据真值表写方程3.3若干常用的组合逻辑电路a.按图3.3.1写出真值表(2)优先编码器YEX=YSSYS[例3.3.1]试用两片74LS148接成16线—4线优化编码器由真值表得出:(1)A15…A8有信号输入时,则A7…A0需禁止有输入信号,即用第(1)片的YS控制第(2)片的S即可实现(2)根据输出规律,利用第(1)片有编码输入时,YEX=0;无编码时,YEX=1,作为数据最高位。取反后作为Z3输出端。根据真值表的分析,两片的同名端的逻辑关系可用“与非”互连。(2)二—十进制优先编码器2.译码器2)真值表(P146表3.3.4)b.74LS138(P146图3.3.8)c)电路图(P146(图3.3.8)2.两片连接方法从真值表看出,D3作为选择端D3=0,控制第(1)片译码器输出,禁止第(2)片;D3=1控制第(2)片译码器输出,禁止第(1)片。D2D1D0为A2A1A0的输入端。(2)二—十进制译码器2)74LS42(P149图3.3.10)②LCDa.原理(P152图3.3.12(a))b.驱动电路(P152图3.3.13)2)BCD—七段显示译码器c.控制端LT=0检查各段能否正确发光;RBI=0灭零输入,把不需显示的零熄灭;BI/RBO作为输入时,灭灯输入控制,作为输出时灭零输出。(4)用译码器设计组合逻辑电路3.数据选择器②CC14539(P160图3.3.21)[例3.3.4]试用两片附加控制端的4选1数据选择器组成一个8选1数据选择器3)逻辑原理图(3)用数据选择器设计组合逻辑电路4.加法器2)全加器①定义在将两个多位二进制数相加时,还考虑来自低位的进位的器件。(2)多位加法器1)串行进位加法器(P166图3.3.8)令:(3)用加法器设计组合逻辑电路5.数值比较器定义用来完成两个二进制数的大小比较的逻辑电路称为数值比较器,简称比较器。(2)多位数值比较器(四位)1)原理(比较器步骤)2)CC145843)逻辑图3.4组合逻辑电路中的竟争—冒险现象2)例二Z=A+A2.检查竟争—冒险现象的方法(3)卡诺图法例Z=AB+AC