如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

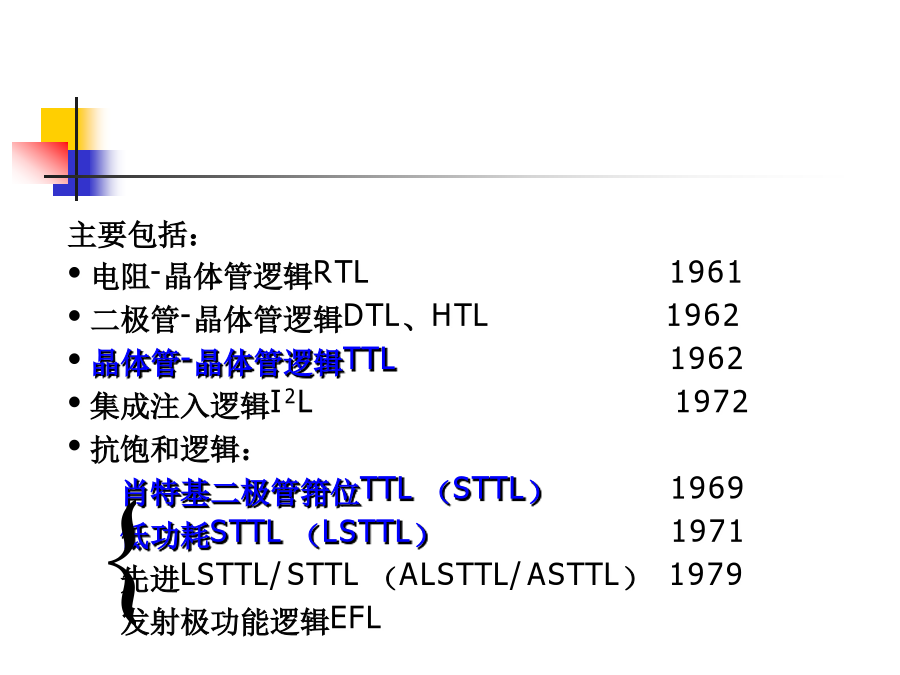

第二章双极型逻辑集成电路本章重点:1、双极集成电路的寄生效应2、TTL、S/LSTTL、AS/ALSTTL、ECL电路的电路结构,工作原理和特点的分析与比较。双极型逻辑IC的分类特点:输出电平稳定逻辑摆幅大电路结构简单功耗较低使用方便由于少子在饱和区存在基区存贮效应,使得开关速度下降主要包括:电阻-晶体管逻辑RTL1961二极管-晶体管逻辑DTL、HTL1962晶体管-晶体管逻辑TTL1962集成注入逻辑I2L1972抗饱和逻辑:肖特基二极管箝位TTL(STTL)1969低功耗STTL(LSTTL)1971先进LSTTL/STTL(ALSTTL/ASTTL)1979发射极功能逻辑EFL非饱和型逻辑IC——关态对应于截止态,而开态对应于线性放大区。特点:无少子存贮效应,工作速度快电路结构复杂逻辑摆幅小功耗较大主要包括发射极耦合逻辑ECL互补晶体管逻辑CTL非阈值逻辑NTL多元逻辑DYL§2.1双极型IC的寄生效应§2.1.1集成npn的结构与寄生效应寄生pnp管处于放大区的三个条件:(1)EB结正偏(即npn管的BC结正偏)(2)BC结反偏(即npn管的CS结反偏)(3)具有一定的电流放大能力(一般pnp=1~3)其中,条件(2)永远成立,因为pn结隔离就是要求衬底P+隔离环接到最低电位。条件(3)一般也很容易达到。条件(1)能否满足则取决于npn管的工作状态。npn管工作于截止区VBC(npn)<0VEB(pnp)<0VBE(npn)<0,VCS(npn)>0VBC(pnp)>0npn管工作于饱和区VBE(npn)>0VBC(npn)>0VEB(pnp)>0VCS(npn)>0VBC(pnp)>0抑制寄生效应的措施:(1)在npn集电区下加设n+埋层,以增加寄生pnp管的基区宽度,使少子在基区的复合电流增加,降低基区电流放大系数;同时埋层的n+扩散区形成的自建减速场也有一定的降低的作用。(2)可采用外延层掺金工艺,引入深能级杂质,降低少子寿命,从而降低。(3)还应注意,npn管基区侧壁到P+隔离环之间也会形成横向pnp管,必须使npn管基区外侧和隔离框保持足够距离。二、集成npn管的无源寄生效应1、抑制无源寄生效应的措施2、等平面工艺与介质隔离3、U型槽隔离§2.2TTL电路的结构特点及工作原理1、电路特点输入级采用多发射极管,在电路截止瞬态(输出高电平),T1对T2基极有很强的反抽作用上升时间r。输入端接反偏二极管,可将输入负向电压箝位在-1.5V(二极管有寄生串联电阻),使电路抗负向脉冲干扰能力提高。输出级采用图腾柱结构(推挽),T3-D1和T5交替工作功耗,速度。由于输出低电平时T5处于饱和态,在向高电平转换时,基区少子存贮电荷只有通过R3泄放,速度较慢,影响上升时间。2、TTL电路的不足与改进措施由上面的分析可见:欲使电路速度tpd=(tpLH+tpHL)/2下降,即tpHL输出管驱动电流,即IB饱和深度超量存贮电荷tpLHtpLH饱和深度IBtpHL采用有源泄放网络,可以部分改善要解决这一矛盾,须在保证较大的驱动电流条件下设法控制晶体管的BC结上的正向偏压,加以箝位,迫使晶体管不进入饱和/深饱和区非饱和或抗饱和TTL电路。2.2.2抗饱和TTL电路——S/LSTTL1、SBD(Schottky-Barrier-Diode)和肖特基箝位晶体管•pn结导通时,都是少子注入积累扩散形成电流,是一种电荷存贮效应,严重影响了pn结的高频特性。•SBD导通时,主要靠半导体多子金属,是多子器件,高频特性好。•对于相同的势垒高度,SBD的JSD或JST要比pn结的反向饱和电流JS大得多,即:对于相同的正向电流,SBD的正向导通压降较低,一般Si为0.3V,Ge为0.2V。根据M-S接触理论,理想情况下WM>WS,金属与n型半导体接触形成阻挡层。WM<WS,金属与n型半导体接触形成反阻挡层。WM<WS,金属与p型半导体接触形成阻挡层。WM>WS,金属与p型半导体接触形成反阻挡层。但实际情况,由于Si,Ge,GaAs等常用半导体材料都有很高的表面态密度,形成表面电荷的“钉扎”现象,不管n型还是p型都形成阻挡层。所以,实际的欧姆接触是利用隧道效应制成的。一般采用PtSi-Ti/W-Al多层金属薄膜系统。其中:•Pt-Si构成SBD•Ti/W——阻止Al与Si相互扩散•Ti(10%)——改善了金属对SiO2的粘附性和抗腐蚀性。2、STTL电路电路特点:优点:•输入端SBD箝位保护,由于导通电压低(0.3V