如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

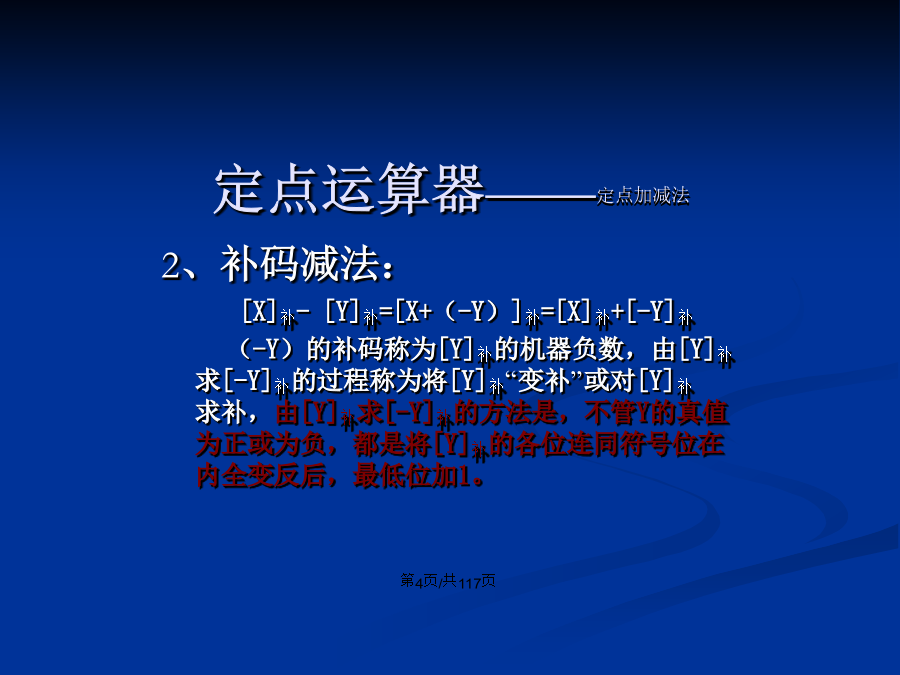

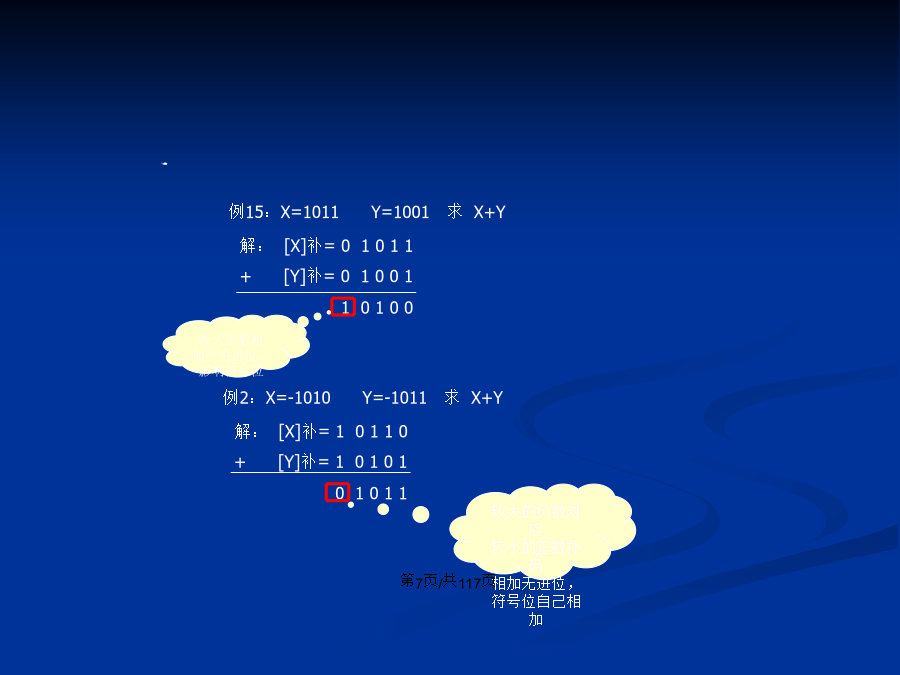

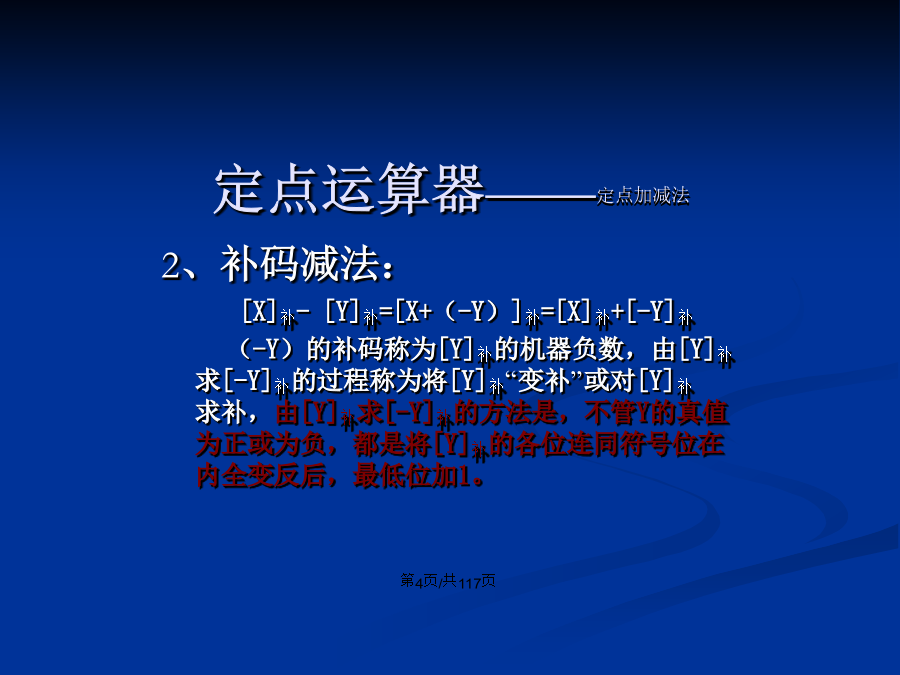

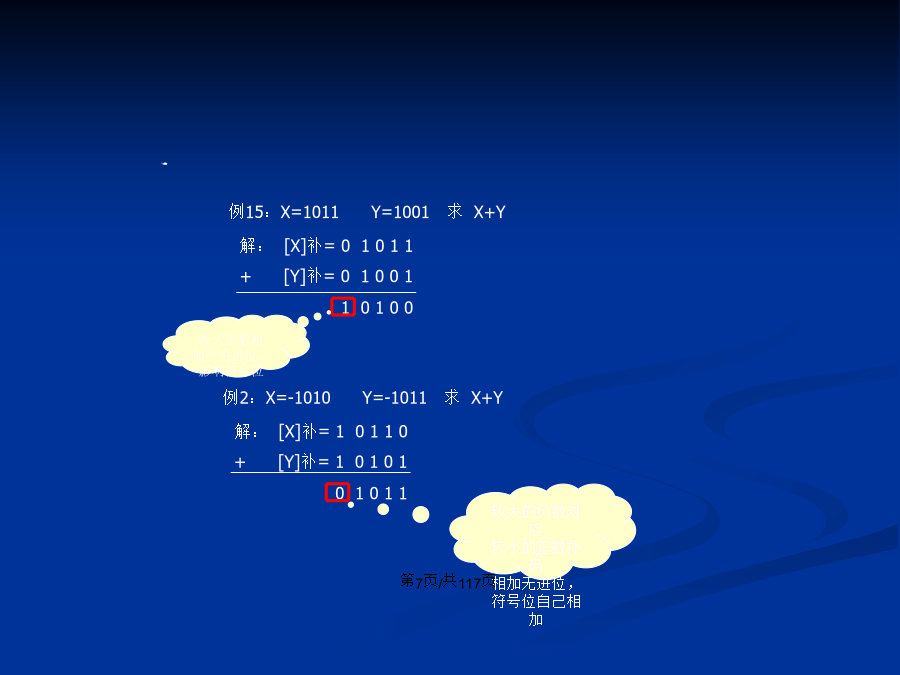

会计学可以证明:[X+Y]补=[X]补+[Y]补[X-Y]补=[X]补+[-Y]补[-Y]补的求法:将[Y]补连同符号位求反加1。例11:X=+1001Y=+0101,求X+Y=?定点运算器——定点加减法定点运算器——定点加减法定点运算器——定点加减法定点运算器——定点加减法3、溢出及其判别方法:(1)、溢出(2)溢出原因:之所以发生错误,是因为运算结果产生了溢出。两个正数相加,结果大于机器所能表示的最大正数,称为上溢。而两个负数相加,结果小于机器所能表示的最小负数,称为下溢。为了判断“溢出”是否发生,可采用两种检测的方法。第一种方法是采用双符号位法,这称为“变形补码”或“模4补码”。从而可使模2补码所能表示的数的范围扩大一倍。定点运算器——定点加减法定点运算器——定点加减法例17:X=+0.1100Y=+0.1000,求X+Y=?解:例:X=-0.1100Y=-0.1000,求X+Y=?解:由此可以得出如下结论:1.当以模4补码运算,运算结果的二符号位相异时,表示溢出;相同时,表示未溢出。2.模4补码相加的结果,不论溢出与否,最高符号位始终指示正确的符号。例:X=-0.100Y=-0.101,求X+Y=?解:例:X=100,Y=-110,求X-Y=?解:4、基本的二进制加法/减法器n个1位的全加器(FA)可级联成一个n位的行波进位加减器。M为方式控制输入线,当M=0时,作加法(A+B)运算;当M=1时,作减法(A-B)运算,在后一种情况下,A-B运算转化成[A]补+[-B]补运算,求补过程由B+1来实现。时间延迟ta=n×2T+9T十进制加法器定点运算器——定点乘法定点运算器——定点乘法定点运算器——定点乘法定点运算器——定点乘法定点运算器——定点乘法(了解)原码并行乘法图2.4m×n位不带符号得阵列乘法器逻辑框图演示动画原码并行乘法演示动画用这种对2求补器来转换一个(n+1)位带符号的数,所需的总时间延迟为tTC=n×2T+5T=(2n+5)T图2.7所示的带求补级的阵列乘法器既适用于原码乘法,也适用于间接的补码乘法。不过在原码乘法中,算前求补和算后求补都不需要,因为输入数据都是立即可用的。而间接的补码阵列乘法却需要使三个求补器。为了完成所必须的求补与乘法操作,时间大约比原码阵列乘法增加1倍例20例21直接补码并行乘法(不做要求)补码与真值的转换公式表2.3四类一般化全加器的名称和逻辑符号直接补码阵列乘法器直接补码阵列乘法器也可以如动画演示所示定点运算器——定点除法定点运算器——定点除法定点运算器——定点除法定点运算器——定点除法恢复余数法定点运算器—定点除法解:被除数/余数商数q说明定点运算器—定点除法定点运算器—定点除法定点运算器—定点除法定点运算器—定点除法解:[X]原=[X]补=X=0.1001,[Y]补=0.1011,[-Y]补=1.0101被除数X/余数r商数q说明并行除法器(不做要求)可控加法/减法(CAS)单元2.不恢复余数的阵列除法器2.不恢复余数的阵列除法器/2.不恢复余数的阵列除法器例23x=0.101001,y=0.111,求x÷y。(步骤参考书本)解:2.5定点运算器的组成2.5.1逻辑运算1.逻辑非运算逻辑非也称求反。如:x1=01001011,x2=11110000,求x1,x2。x1=10110100x2=000011112.逻辑加运算按位求它们的“或”x=10100001,y=10011011,求x∨y。10100001x∨10011011y10111011z3.逻辑乘运算按位求它们的“与”x=10111001,y=11110011,求x∧y。10111001x∧11110011y10110001z4.逻辑异运算按位求它们的模2和x=10101011,y=11001100,求x⊕y。[解:]10101011x⊕11001100y01100111z即x⊕y=01100111事实上,逻辑加还可以通过逻辑乘和逻辑非来实现:同样,逻辑乘也可以用逻辑加和逻辑非来实现:2.5.2多功能算术/逻辑运算单元(ALU)定点运算器的组成——多功能算术/逻辑运算单元定点运算器的组成——多功能算术/逻辑运算单元定点运算器的组成——多功能算术/逻辑运算单元定点运算器的组成——多功能算术/逻辑运算单元用正逻辑表示的4位算术/逻辑运算单元(ALU)的逻辑电路图如下,它是根据上面的原始推导公式用TTL电路实现的。这个器件的商业标号为74181ALU。/两级先行进位先行进位部件74182CLA所提供的进位逻辑关系如下:Cn+x=G0+P0CnCn+y=G1+P1Cn+x=G1+G0P1+P0P1CnCn+z=G2+P