如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

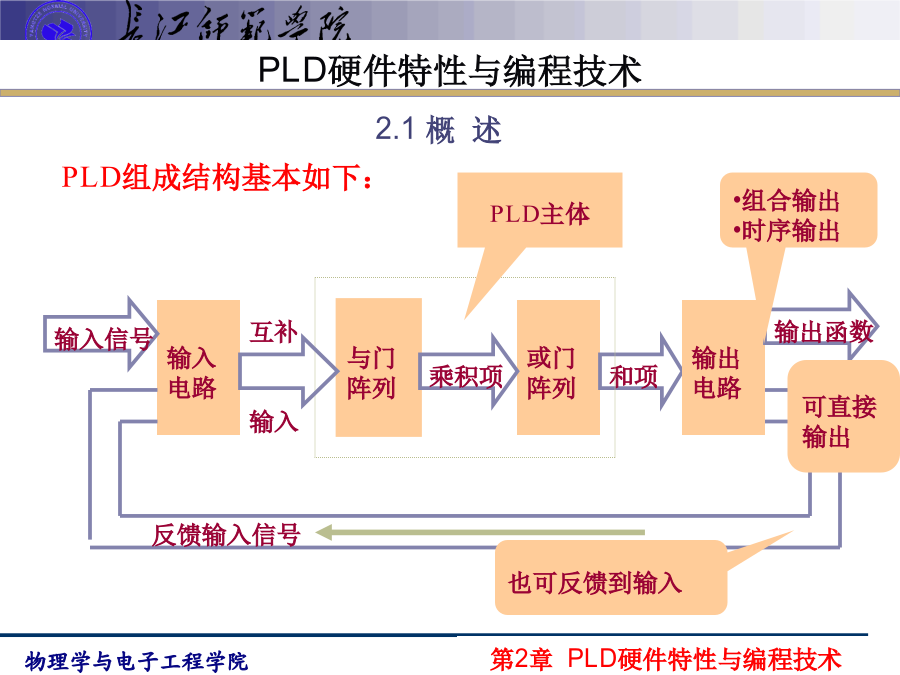

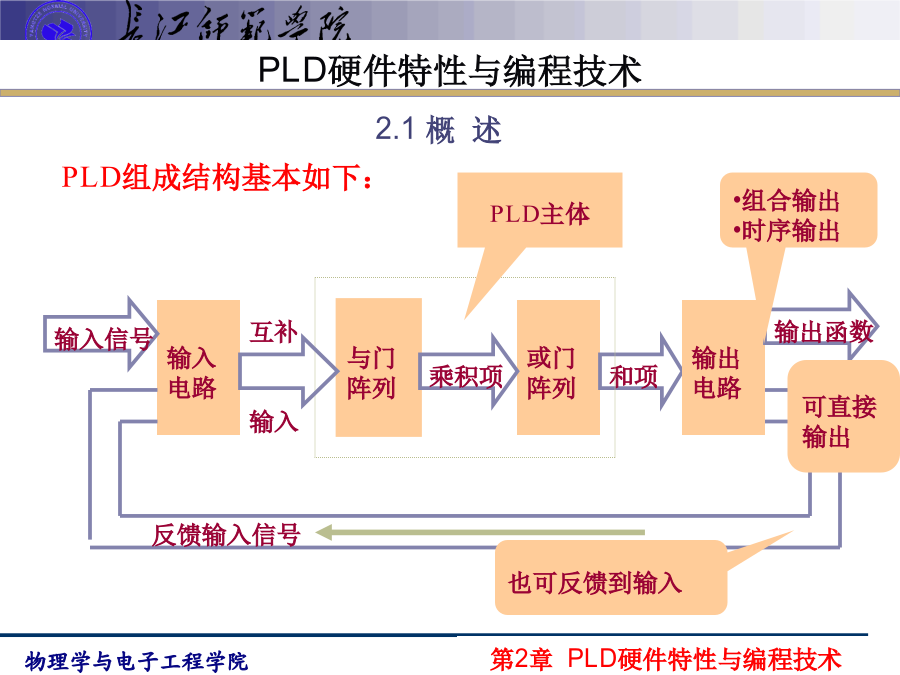

教学重点一、什么是PLD?1.什么是PLD?PLD:ProgrammableLogicDevice,可编程逻辑器件2.PLD的特点(1)编程方便:利用开发工具,用户可反复编程、擦除,修改设计方便(2)集成度高:单片逻辑门数已达数十万门甚至上百万门(3)速度快(4)价格低(5)开发周期短:EDA开发工具齐全,设计人员在很短时间内可完成电路设计的输入、编译、仿真和编程,大大缩短了开发周期。PLD硬件特性与编程技术工艺线宽:由于生产工艺的发展,PLD集成电路的工艺线宽可达到0.35m(1997年),0.15m(2001年),0.13m(2002、2003年),0.1m(2004年);90nm(2005年);目前半导体公司正重点研发60nm工艺。集成度:在一块硅片上可集成上千万个以上逻辑门。速度:器件的速度指标↑,FPGA的门延时﹤3ns,CPLD的系统速度﹥180MHz。工艺手段:CMOS工艺在速度上超过双极型工艺,成为PLD的主要工艺手段。三、EDA技术与PLD的关系PLD的应用开发过程中贯穿着EDA技术的应用PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术PROM基本结构PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术例:用PLA实现逻辑函数用PLA实现三八译码器PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术例:Y=ABC,用PAL阵列实现该式。PLD硬件特性与编程技术PLD硬件特性与编程技术PLD硬件特性与编程技术1.GAL输出逻辑宏单元OLMC的组成PLD硬件特性与编程技术2.OLMC的三种输出结构复合模式简单模式可编程与阵列4GAL器件优点(4)高性能的E2COMS工艺:GAL的高速度、低功耗,编程数据可保存20年以上。5GAL器件缺点2.3CPLD结构与工作原理复杂PLD,根据器件互连结构、逻辑单元结构分为:将整个器件划分为若干个区域,每个区域相当于一个GAL,通过全局互连总线将各个区域连接起来。4.3CPLD结构与工作原理共享相邻乘积项和的结构2.“隐埋”触发器结构≥1三、分区阵列结构的CPLD通用互连阵列UIM结构多阵列矩阵MAX结构1.通用互连阵列UIM结构(UniversalInterconnectMatrix)FFB和FB都采用GAL型结构。FFB适用于快速编(解)码和高速时序逻辑电路;FB适用于逻辑功能复杂且对时序要求不高的场合及复杂的组合逻辑电路。2.多阵列矩阵MAX结构(MultipleArrayMatrix)PIA多阵列矩阵MAX结构MAX7000S器件的宏单元结构MAX7000S器件的宏单元结构共享扩展乘积项结构并联扩展项馈送方式可编程连线阵列(PIA)I/O控制块2.4FPGA结构与工作原理目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1的RAM。4输入LUT内部结构图4输入与门的例子当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM。二、FLEX10K系列器件FLEX10K结构中提供了两种专用高速数据通道,用于连接相邻的LE,但不占用局部互连通道。它们是进位链和级联链。级联链可实现最小时延的多输出逻辑函数。相邻的LUT用来并行地完成部分逻辑功能,级联链把中间结果串联起来。Cyclone器件的LE结构(普通模式)2.逻辑阵列块(LAB)3.快速通道互连(FastTrack)4.I/O单元与专用输入端口5.嵌入阵列块(EAB)用EAB构成不同结构的RAM和ROMEAB的大小灵活可变通过组合EAB可以构成更大的模块存储器容量(单位:Bit)1)结构上的不同CPLD与FPGA的主要区别在于逻辑块(逻辑单元)的构成不同:FPGA的基本逻辑单元如:EPF10K10含576个逻辑单元2)集成度的不同CPLD:500-50000门;FPGA:1K–100M门3)应用范围的不同CPLD逻辑能力强而寄存器少(1K左右),适用于控制密集型系统;FPGA逻辑能力较弱但寄存器多(100多K),适于数据密集型系统。2.5CPLD/FPGA测试技术引脚边界扫描数据移位方式2.6产品概述一、ALTERA多阵列矩阵(MultipleArrayMatrix)内部结构:可编程的“与”阵列和固定“或”阵列实现逻辑功能。