如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

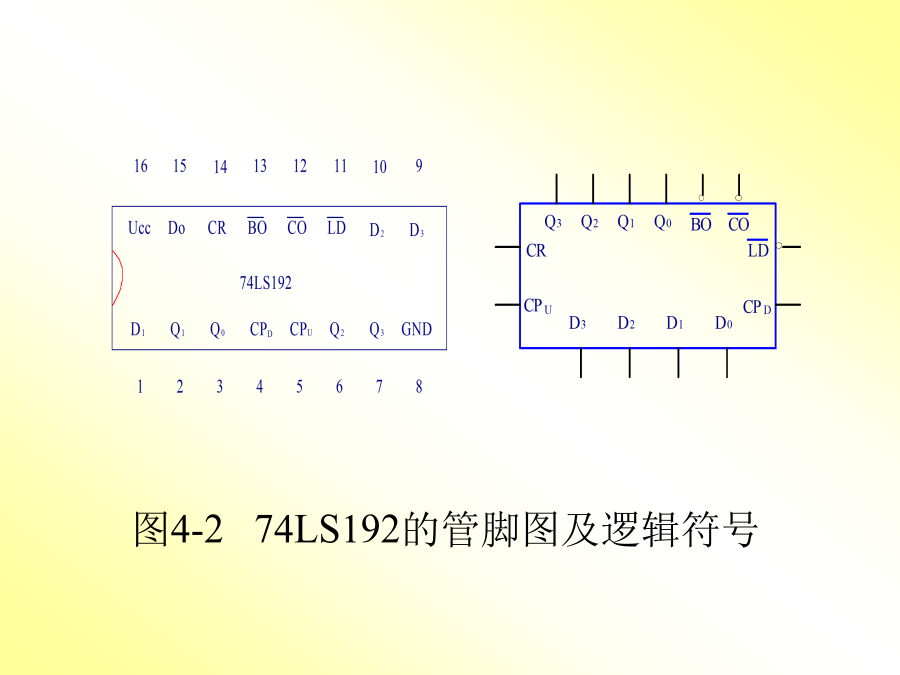

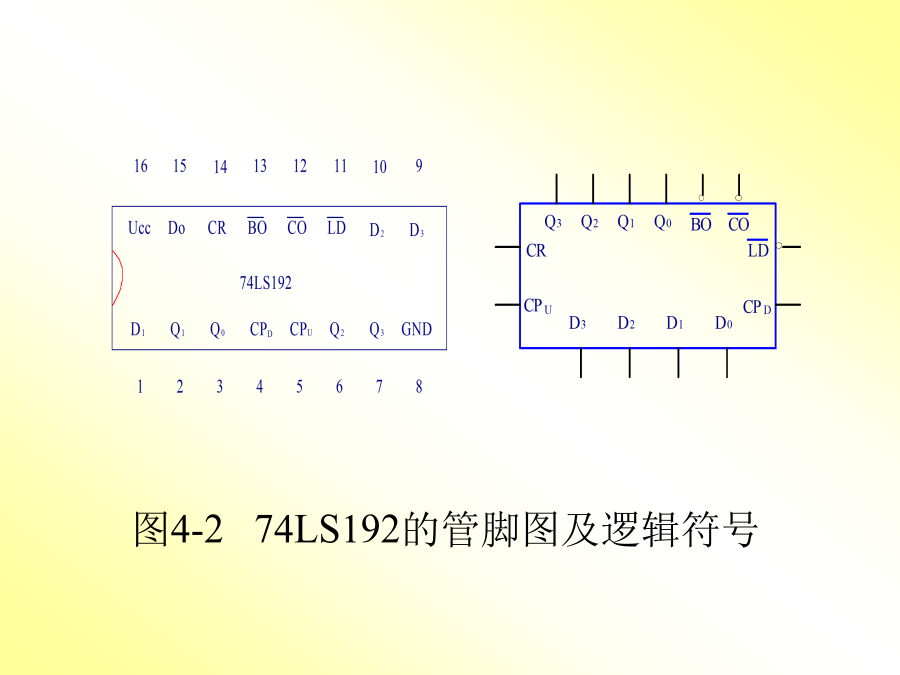

一、实验目的:二、实验原理计数器的种类很多,按构成计数器中各触发器时钟端连接的方式分为同步计数器和异步计数器两类;按计数器的进制又分为二进制计数器、十进制计数器和其它任意进制计数器;按其计数过程中计数状态的变化的情况又可分为加法计数器、减法计数器或可逆计数器。除此之外,计数器还具有可预置数及可编程等功能。实际应用中可以用集成触发器,采用时序电路的构成方法,构成计数器;也可以用中规模集成计数器根据应用需要构成任意进制的计数器。目前,中规模集成计数器无论是TTL结构,还是COMS结构的,种类型号都相当齐全,使用也很方便。1、触发器构成的计数器图4—1是用四个D触发器构成的四位二进制异步加法计数器。其输出为四位二进制编码,在连续时钟CPO作用下,其输出状态编码的变化规律是从Q3Q2Q1Q0=0000~1111递增变化并循环,实现四位二进制的加法计数功能。图4—1触发器构成的四位二进制异步加法计数器2、中规模集成计数器其中:D0、D1、D2、D3——置数并行数据输入;Q0、Q1、Q2、Q3——计数数据输出;CR——清零端;LD——置数端;CPU——加法计数CP输入;CPD——减法计数CP输入;CO——进位输出端;BO——借位输出端;表22-174LS192功能表3、任意进制计数器图4-3反馈清零法构成的6进制计数器图4-4以两位十进制形式输出的8421BCD码12进制计数器三、实验内容与步骤2、74LS192同步可逆递增/递减BCD计数器功能测试给集成电路的电源端加工作电源,CP端接入1Hz连续脉冲,CR端、LD端、D3D2D1D0端分别接逻辑开关,输出Q3Q2Q1Q0接8421译码显示接口的D、C、B、A;按表4--1逐项测试集成计数器的各项功能。3、用反馈法将两片74LS192构成一个60进制计数器。四、实验仪器及元器件五、实验报告要求