如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

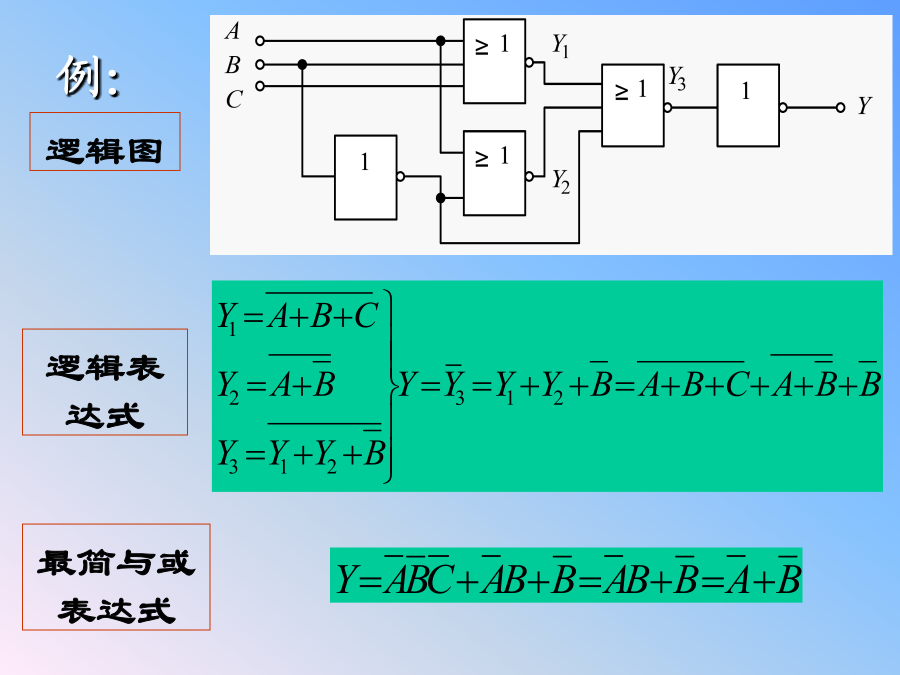

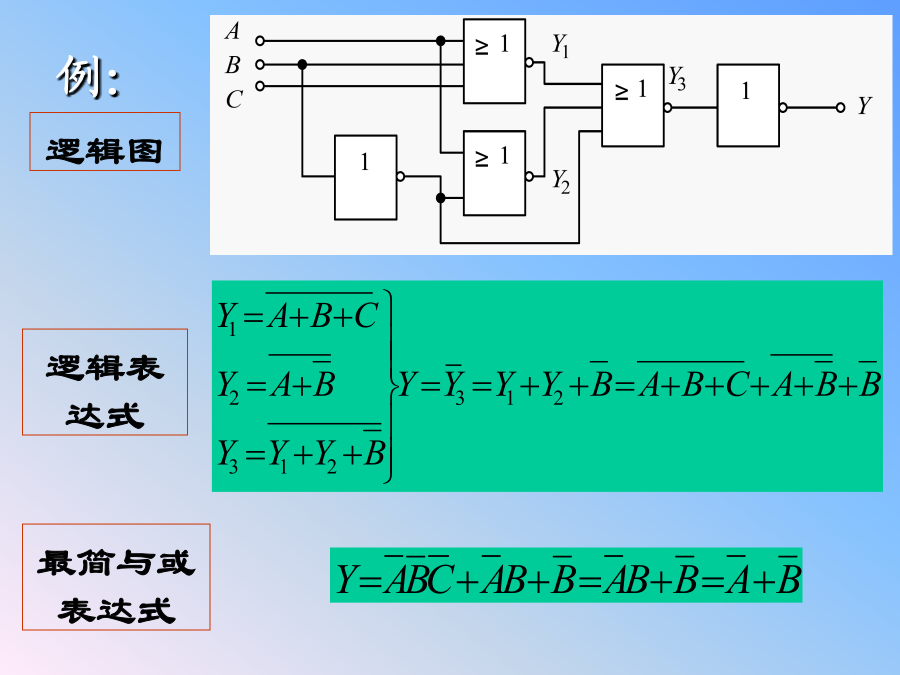

第17章组合逻辑电路117.1组合逻辑电路的特点17.2组合逻辑电路的分析与设计方法17.2.1组合逻辑电路的分析方法最简与或表达式逻辑图真值表真值表2真值表3本节小结17.3加法器和数值比较器一、半加器二、全加器全加器的逻辑图和逻辑符号用与门和或门实现实现多位二进制数相加的电路称为加法器。为提高速度,必须设法减少或消除进位信号进行传递消耗的时间.加到第i位的输入信号Ci是两个加数第i位以前的二进制函数.进位:有两种情况(1)(2)第i位相加产生的进位输出2、并行进位加法器(超前进位加法器)超前进位发生器集成二进制4位超前进位加法器本节小结用来完成两个二进制数的大小比较的逻辑电路称为数值比较器,简称比较器。逻辑表达式二、多位数值比较器真值表中的输入变量包括A3与B3、A2与B2、A1与B1、A0与B0和A'与B'的比较结果,A'>B'、A'<B'和A'=B'。A'与B'是另外两个低位数,设置低位数比较结果输入端,是为了能与其它数值比较器连接,以便组成更多位数的数值比较器;3个输出信号L1(A>B)、L2(A<B)、和L3(A=B)分别表示本级的比较结果。逻辑图